# EOT sub-nanométrico y degradación de la movilidad: ¿hacia un límite físico con las técnicas de fabricación modernas?

Lionel Trojman<sup>1\*</sup>, Luigi Pantisano<sup>2</sup>, José Bustamante<sup>1</sup>, Santiago Navarro<sup>1</sup>

<sup>1</sup>Colegio de Ciencias e Ingeniería - El Politécnico, Universidad San Francisco de Quito. Diego de Robles y Vía Interoceánica, Quito, Ecuador

<sup>2</sup> Interuniversity MicroElectronic Center, IMEC.

Kapeldreef 75, B-3001, Leuven, Belgium

\*Autor principal/Corresponding author, e-mail: ltrojman@usfq.edu.ec

Editado por/Edited by: R. Játiva, M.Sc.

Recibido/Received: 03/17/2010. Aceptado/Accepted: 04/29/2010.

Publicado en línea/Published on Web: 05/23/2010. Impreso/Printed: 06/01/2010.

#### **Abstract**

In this article we investigate the major problem of the micro/nano-electronic: How to reduce the Equivalent Oxide Thickness (EOT) in the sub-nanometric range and improving the MOSFET performance? To reduce the EOT it is necessary that the semiconductor industry introduce the high- $\kappa$  material as the Hafnium (Hf) in the dielectric layer. However the Hf produces a reduction of the mobility and therefore a reduction of the MOSFET speed. We explain through a simple semi-empirical model this mobility degradation in order to familiarize the reader with the concept of mobility for the high- $\kappa$  MOSFET. Afterward we focus on two optimized processing methods for the EOT reduction yielding the best gate stack quality. These processing methods are the Fully-Silicide (FuSi) gate with HfSiON dielectric and the Metal Gate with HfO2 which are both "gate first" based integration scheme. The important results we found is that first we can obtain a sub-1nm EOT in the both cases although it was thought impossible to make it with high thermal budget process such as the FuSi method. Second, the mobility degradation is very similar in the both case in spite of the very different chemistries we use to form the gate stack. We conclude that the modern deposition technique does not allow controlling the dielectric quality as of 0.8 nm and we suggest using the "gate last" based integration scheme to improve further the gate stack quality.

**Keywords.** Microelectronics, MOSFET, high- $\kappa$ , sub-1nm EOT, mobility, Coulombic interaction.

## Resumen

En este artículo investigamos un problema mayor de la microelectrónica moderna. Para reducir el EOT y aumentar el desempeño del MOSFET, la industria tiene que introducir el material high- $\kappa$ , como el Hf. Pero eso genera una degradación de la movilidad y una pérdida de la rapidez de los dispositivos. Explicamos esta degradación con un modelo muy sencillo para familiarizar al lector con el concepto de movilidad. Después nos enfocamos en dos procesamientos optimizados (Fully-Silicid con HfSiON y Metal Gate con HfO2) para reducir el EOT y causar un mínimo de defectos en el film. Un resultado muy importante es que podemos lograr un EOT sub-nanométrico en los dos casos ya que esto fue considerado imposible con el FuSi/HfSiON. Otro resultado importante es que en los dos casos la degradación de la movilidad es muy parecida a pesar de que los dos procesamientos generan una pila de compuerta de naturaleza química muy diferente. Concluimos que con las técnicas de deposición moderna no se controla la calidad del dieléctrico a partir de 0.8 nm y sugerimos cambiar el esquema de integración con un "gate last".

**Palabras Clave.** Microelectrónica, MOSFET, high- $\kappa$ , EOT sub-nanométrico, movilidad, interacciones Coulómbicas.

### Introducción

Hace más de 50 años que los dispositivos del estado sólido han revolucionado las sociedades humanas en casi cualquier aspecto de la vida cotidiana. La computado-

ra y el teléfono celular son simplemente dos ejemplos de su impacto. En medio de todos los dispositivos, el MOSFET [1] es el dispositivo que ha jugado el rol protagónico en las tecnologías modernas (memoria, aplicación lógica etc.) por medio de los circuitos integrados

[2] y gracias a el "scaling" o la miniaturización [3, 4]. Sin embargo, la reducción de las dimensiones verticales, o de la "Equivalent Oxide Thickness (EOT)", del MOSFET hecho con Si/SiO<sub>2</sub> o Si/SiON, se acerca de 1nm lo que impone un límite físico que no permite garantizar el desempeño de los MOSFET de la generación a venir. Los principales problemas son la degradación de la capacitancia y el aumento de la corriente de la compuerta ("Gate") [5]. De este modo la solución más realista conduce a cambiar el SiO2 o SiON por un material llamado de "alta constante dieléctrica". Nos referiremos a ellos como materiales de high- $\kappa$ . Entre todos los materiales high- $\kappa$ , el dióxido de hafnio (HfO<sub>2</sub>) esta considerado como la mejor opción [5]. En el MOSFET con high- $\kappa$  la estructura vertical (o gate stack) es de tipo multi-capas. Tenemos una capa de Interfacial Oxide Thickness de IOT = 0.4-1 nm hecha con  $SiO_2$  debajo de un capa de material high- $\kappa$  (1-4 nm de HfO<sub>2</sub>) y de un compuerta hecha con metal (TiN o TaN) como lo muestra Tsai et al. [6]. Con este tipo de estructura podemos alcanzar un EOT = 0.8 nm, con una densidad de corriente de compuerta  $J_G = 1A/cm^2$ , lo que es menor en un factor 3 al MOSFET con SiO<sub>2</sub> puro [5]. Pero Ragnarsson el al. [7] encontraron también una degradación de la movilidad de los portadores con los MOS-FET high- $\kappa$  cuando reducimos su EOT. Esta degradación se explica por una reducción del efecto de apantallamiento que a su vez disminuye las interacciones entre los portadores de carga y los defectos eléctricos contenidos en la capa high- $\kappa$  o a las interfaces de la capa de high- $\kappa$  [8]. La densidad de estos defectos depende del método de procesamiento. Por ejemplo podemos usar menos Hf para tener menos defectos [9] pero eso va a reducir el valor de la constante dieléctrica ( $\kappa$ ) y en teoría reducir la posibilidad de obtener un EOT fino (1nm) [5]. En este artículo hacemos una investigación de métodos de procesamiento optimizados, y comparamos el máximo de movilidad que podemos lograr para un EOT sub-nanométrico en cada caso. Para empezar vamos a explicar la degradación de la movilidad por medio de las interacciones Coulómbicas con un nuevo y sencillo modelo semi-empírico. Después vamos a detallar dos métodos de procesamiento optimizados para el material high- $\kappa$  y basados en el esquema más usado en la industria, llamado "gate first/last" o "gate first". El primer método es el "Fully Silicide (FuSi)" con Hf-SiON (o Fusi/HfSiON) que se realiza a alta temperatura (1000 °C). El segundo, "Metal Gate (MG)" con HfO<sub>2</sub> (o MG/HfO<sub>2</sub>) se puede realizar a baja temperatura. Finalmente vamos a comparar las dos tecnologías y encontrar que llegamos a una límite físico de reducción de EOT también con el Hafnio y que eso no depende del tipo de procesamiento.

### Metodología

## Método Procesamiento de los dispositivos

Lo dispositivos high- $\kappa$  que vamos a estudiar están hechos con las tecnologías descritas a continuación. Los

wafers están hechos de Si con dopaje tipo p, de 200 mm de diametro, cortado en el plano (100) y los transistores son integrados en la dirección  $\langle 110 \rangle$  con el método llamado "self-aligned".

En el caso del FuSi, preparamos el wafer con el "In-Situ-Steam-Generation (ISSG)" [10] para hacer crecer una capa de 0.4-0.5 nm de SiO<sub>2</sub>. Después eso depositamos una capa de  $HfSiO_X$  por medio de "Metal Organic Chemical Vapor Deposition (MOCVD)" [11] (con 60 % de Hf) a 650 °C. El nitrogenó es introducido por medio de un "Decoupled Plasma Nitridation (DPN)" y de un "Post Nitradation Annealing (PNA)" a 900 °C con O<sub>2</sub> [12]. Una capa de Poly-Si (100 nm) es depositada sobre la capa de HfSiON con "Chemical Vapor Deposition (CVD)" a 700 °C. Después de esta operación la uniones "Source/Drain (S/D)" son activadas con un Spike Annealing (1000 °C, 1s). Una vez que los contactos están hechos, una capa de Ni es depositada sobre la compuerta y con dos "Rapid Thermal Processing (RTP)" formamos una compuerta hecha de NiSi o FuSi [13]. El caso del MG, la preparación de la superficie del wafer se hace con un IMEC clean o IMEC'04 [14]. El HfO<sub>2</sub> se deposita con "Atomic Layer Deposition (ALD o ALCVD $^{TM}$ )" (1.8 a 3 nm, 300 °C)[15] y también la compuerta TaN/TiN (12 nm/100 nm) [16] con PVD a temperatura ambiente. Antes de formar la compuerta aplicamos un "Degas" sea a T=350 °C o a T=450 °C [17] para reducir la concentración de H2O. La activación de las uniones se hace posteriormente con el método "Solid Phase Epitaxial regrowth (SPER)" (650 °C, 1min)[18] o con el método Spike. El procesamiento MG corresponde a un esquema de integración llamado "gate first" y el FuSi, "gate first/last" [19]. En los dos casos la capa de high- $\kappa$  se deposita posteriormente a la activación de las uniones para satisfechar los requisitos de la industria de la microelectronica. En este estudio nos enfocamos sólo sobre los n-MOS (los portadores de carga son electrones).

### Método de caracterización eléctrica

En este trabajo el método descrito en [20] que consiste en extraer la movilidad con la característica de la corriente (I-V) y la medición de la capacitancia (C-V). Para el C-V usamos el método llamado "Split-CV", ya sea básico [21] o avanzado ("RF Split CV" [22]).

Los efectos de las resistencias en serie están corregidos con la Ecuación 1:

$$R_{CH} = \frac{V_{DS}}{I_{DS}} - R_S \tag{1}$$

donde  $I_{DS}[A]$  es la corriente fuente-a-drenaje,  $V_{DS}=50mV$  la caída de potencial entre la fuente y el drenaje  $R_{CH}[\Omega-cm]$  es la resistencia del canal o intrínseca y  $R_S$  es la resistencia en serie o parasítica.

La movilidad efectiva se ha obtenido por medio de la siguiente Ecuación:

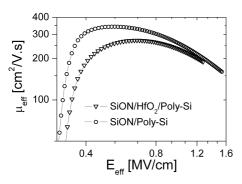

Figura 1: Ejemplo de extracción de la movilidad y comparación de la movilidad entre un dispositivo de tipo high- $\kappa$  y SiON.

$$\mu_{eff}(V_G) = \frac{L}{W} \frac{I_{DS}(V_G)}{V_{DS}} \frac{1}{Q_S(V_G)}$$

(2)

donde  $Q_S=qN_S[C/cm^2]$  es la carga de inversión ( $q=1,6021\times 10^{-19}C$  es la carga de Coulomb) , L[cm] la longitud y W[cm] el ancho del canal. La carga de inversión se deduce de la capacitancia en regimen de inversión medida con el método Split-CV.

La extracción del campo efectivo se ha obtenido con la Ecuación 3 [20]:

$$E_{eff}(V_G) = \frac{Q_{DEP} + \eta Q_S}{\epsilon_{Si}} \tag{3}$$

donde  $\epsilon_{Si}$  es la permitividad dielectrica del Si ( $\approx 1.04 \times 10^{-12} F/cm$ ),  $Q_{DEP}$  es la carga de agotamiento, y  $\eta$  describe la contribución de la  $Q_S$  en el campo eléctrico efectivo o vertical [20]. Un ejemplo de la extracción de la movilidad está dado en la Figura 1. Las explicaciones de la degradación están dadas en el párrafo siguiente.

La extracción de la IOT se ha hecho con los datos de la C-V, para los dispositivos HfO<sub>2</sub>. En el caso del MG/HfO<sub>2</sub> el valor nominal es muy diferente del valor real debido a un recrecimiento con la temperatura de la activación de las uniones [23, 17]. La ecuación para la IOT es:

$$IOT = EOT - \left(\frac{\epsilon_{SiO_2}}{\epsilon_{h\kappa}}.t_{h\kappa}\right) \tag{4}$$

donde la permitividad relativa del SiO<sub>2</sub> es 3.9 ( $\epsilon_{SiO_2}$ ) y 20 para el HfO<sub>2</sub> ( $\epsilon_{h\kappa}$ ) [24]. El espesor físico de la capa high- $\kappa$  es  $t_{h\kappa}[nm]$ . El EOT se ha obtenido con el algoritmo de "fitting" desarollado por Hauser *et al.* [25]

## Resultados y Discusión

## Evidencia de las interacciónes Coulómbicas

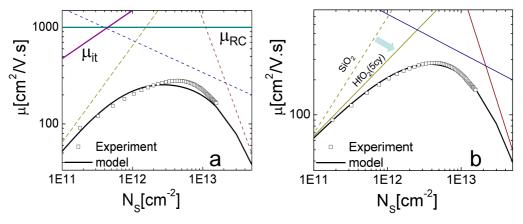

Como lo explicamos en la introducción, la degradación de la movilidad (Figura 1) viene de una interacción entre los portadores de carga y los defectos eléctricos de la capa de  $HfO_2$ . En la Figura 2 se muestra la movilidad de un dispositivo high- $\kappa$  con capa de SiON de 2-1.5

nm con menos de una mono-capa de HfO<sub>2</sub> (5 ciclos con ALD) [26]. De esta manera podemos considerar que las colisiones producidas por "Remote Phonons Scattering (RPS)" [27] son muy débiles en comparación de las colisiones producidad por "Remote Coulomb Scattering (RCS)" o interacciónes con defectos eléctricos producidos por la capa de high- $\kappa$ . Recordemos que las colisiones de los portadores de carga en el MOSFET dependen del campo vertical o campo efectivo en régimen óhmico. Las interacciónes en campo débil son de naturaleza Coulómbica de tal manera que el efecto de los defectos del high- $\kappa$  debería observarse sólo en campo débil.

Basado en la regla de Matthiessen y de las ecuaciones semi-empirícas de cada intereacción [28] podemos dar una descripción más detallada de las interacciones en campo débil (Figura 2a). Pero decidimos proponer también un nuevo modelo semi-empirico más adecuado a nuestro caso. De este modo las interacciones tanto de los RCS y las impurezas ionizada como de los defectos en la interface Si/SiO<sub>2</sub> están descritos con solo una ecuación:

$$\mu_C^* = a_1' N_S^{\delta'}.T \tag{5}$$

donde  $a_1'$  y  $\delta'$  son constantes empirícas, T[K] es la temperatura.

En esta ecuación los dos tipos de interacción Coulómbica (RCS y defectos de interface) son descritos como una reducción del efecto de apantallamiento de la carga inversa del canal del MOSFET. Así obtenemos un modelo de la movilidad efectiva más preciso (Figura 2b). La comparación entre un dispositivo de Si/SiO<sub>2</sub> y Si/SiO<sub>2</sub>/HfO<sub>2</sub> (Figura 1) muestra que la movilidad en campo débil es más alta cuando no hay Hf en la pila de compuerta del MOSFET. En consecuencia el tiempo entre dos colisiones de los portadores de carga es más largo cuando no hay Hf. Este fénomeno nos conduce a conlcuir que se produce un aumento en las interacciónes en campo débil debido a los defectos eléctricos producido por la capa de HfO<sub>2</sub>.

La reducción de los defectos Coulómbicos depende del método de deposición del high- $\kappa$  como lo vamos a mostrar en los párrafos siguientes.

### El compromiso Hf/EOT

El uso del Hf es positivo para reducir el EOT y mantener un nivel de corriente de compuerta suficientemente bajo en relación con las especificación de la ITRS [29]. Pero al mismo tiempo encontramos una degradación de la movilidad, negativa para la rapidez de funcionamiento del MOSFET. El problema de la degradación es causado físicamente por la reducción del tiempo de colisión de los portadores como lo explicamos en el párrafo pasado. Para reducir los defectos eléctricos de la capa de Hf podemos sea reducir la cantidad de Hf o modificar el método de procesamiento en términos de temperatura.

Figura 2: La movilidad para diferentes tipos de interacciones: Coulómbicas en campo débil, phonones en campo medio y rugosidad de interface en campo fuerte de acuerdo con [20]. Las interacciones con defectos de interface están dada por  $\mu_{it}$  y con defectos dentro la pila high- $\kappa$  o RCS por  $\mu_{RC}$ . De acuerdo con la Ec. 2 el campo es proporcional a la densidad de la carga de inversión N $_S$ . En a, las interacciones están descritas con un modelo complicado y no permite obtener una buena descripción de la movilidad efectiva. En b usamos un modelo más sencillo (Ec. 5) y obtenemos una mejor precisión para la descripcion de la movilidad efectiva.

En el caso de un dispositivo de puro HfO<sub>2</sub>, el control de la temperatura y de la concentración de H<sub>2</sub>O (con la temperatura del "Degas"), es muy importante para reducir la cantidad de defectos [17] y obtener un EOT más fina. De hecho una temperatura demasiado alta ( $\geq 650$ °C) genera una recristalización de la capa de HfO<sub>2</sub> [30]. Pero la temperatura y la concentración de H<sub>2</sub>O (gas precursor de ALD) también genera un recrecimiento del espesor de la capa de SiO2 (IOT) que reduce una parte la posibilidad de tener un EOT fino [23] y de otra parte la calidad de la interface SiO<sub>2</sub>/HfO<sub>2</sub> [17], sobre todo para T≥ 900 °C [31]. En un trabajo anterior [17] concluimos que un dispositivo con HfO2 tiene que ser procesado a una temperatura menor o igual a 650 °C y con una concentración de H<sub>2</sub>O muy baja. La Tabla 1 sintetiza este resultado.

En el caso del HfO $_2$  el recrecimiento del SiO $_2$  hace aumentar el EOT . Entonces el procesamiento que tiene un menor "thermal budget" y con un "Degas" a T=450 °C será preferido. Por esta razón tenemos que usar una activación de unión de tipo SPER que trabaja a 650 °C en lugar de un Spike. No obstante la reducción de la capa de SiO $_2$  genera más interacción entre los portadores de carga y los defectos eléctricos en la interface SiO $_2$ /HfO $_2$  y dentro la capa de HfO $_2$ . Además los esquemas de integración usados en industria moderna necesitan una activación de tipo Spike (mejor calidad de las uniones S/D).

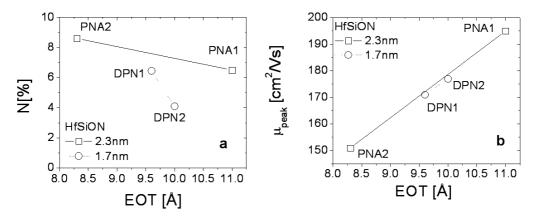

La otra opción es de disminuir la cantidad de Hf y usar una capa high- $\kappa$  hecha con una aleación de HfSiON en su lugar. La ventaja de esta aleación es que el N permite que la capa tenga una estabilidad con respecto a la temperatura cerca del SiO2. Pero el valor  $\kappa$  del HfSiON ( $\approx$  12) es inferior al HfO2 ( $\approx$  20). Eso significa que no podemos alcanzar EOT del mismo espesor con los dos tipos de materiales high- $\kappa$  en teoría; los EOT más finos se han observado con dispositivos hechos de HfO2 (EOT  $\approx$ 0.8 nm) [23, 6]. Sin embargo si usamos condiciones de PNA en las cuales la presión parcial de O2 es más baja (ver Tabla 2) obtenemos un dispositivo

| Thermal Budget                     | SPER   | SPER   | Spike  |

|------------------------------------|--------|--------|--------|

| Degas                              | 450 °C | 350 °C | 450 °C |

| peak $\mu$ [ $cm^2/V.s$ ]          | 260    | 250    | 240    |

| $N_{ot}[10^{12}cm^{-2}]$           | 1.2    | 1.3    | 1.6    |

| (PIV)                              |        |        |        |

| $N_{bulk}[10^{10}cm^{-2}.cy^{-1}]$ | 0.8    | 0.87   | 1      |

| (CP)                               |        |        |        |

Tabla 1: Lista de la densidad de defectos en la pila TiN/TaN/HfO $_2$  extracta con dos tecnicas, "(Pulse-IV (PIV)" y "Charge Pumping (CP)" y del pico de la movilidad efectiva por disposotivos con la misma IOT y EOT. La mejor movilidad esta en correlación con la menor densidad de defetos (SPER+450  $^{\circ}$ C).

HfSiON con una compuerta de FuSi que tenga una EOT  $\approx$ 0.8 nm (Figura 3a). La concentración de N permite aumentar el valor del  $\kappa$  del HfSiON [12] así que podemos alcanzar un EOT muy fino también con este tipo de procesamiento (alta temepratura o "high thermal budget"). Tenemos que tomar también en cuenta el efecto del N en la capa de SiO<sub>2</sub>. De acuerdo con [32] el N impide un recrecimiento de la IOT debido a su propiedad de reducción. No obstante el N puede contaminar la capa de interface y generar un material más cerca del SiON que del SiO<sub>2</sub>. El SiON tiene un valor de  $k \approx 7$  que es más alta que para el SiO<sub>2</sub> y eso contribuye seguramente a reducir el EOT. La reducción de la presión parcial de O<sub>2</sub> durante el PNA, ayuda también a una mejor introducción del N en la pila de la compuerta como lo indica la concentración proveída por la medición "X-ray Photoelectron Spectroscopy (XPS)" (Figura 3a).

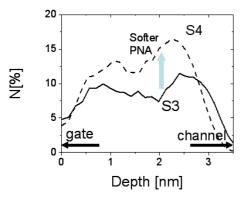

El aumento de N genera también una degradación de la movilidad como lo muestra la Figura 3b, tal como se ha reportado en [33]. Se supone que el N genera interacción Coulómbica con los portadores de carga en el canal y este efecto se vuelve más importante cuando el N se encuentra cerca del la interface Si/SiO₂. En un dispositivo con EOT≈0.8 nm, el experimento XPS muestra también un perfil de N más cerca de la interface (Figura 4) sugiriendo una penetración más importante del N

Figura 3: a muestra la correlación entre la reducción del EOT y el aumento de la concentración de N. A partir de 8 % de N se obtiene un valor de  $\kappa$  suficiente alta para alcanzar una EOT de 0.8 nm usando una interfaz de SiO $_2$  con una activación de las uniones de 1000  $^{\circ}$ C. b muestra la caída de movilidad que está en correllacion con la reduccion de EOT debido a un aumento de la concentracion de N.

Figura 4: Perfil de N para el dispositivo con el mayor espesor de HfSiON. Se oberva un pico de N en la dirección del canal, sugiriendo una concentración más importante cerca del canal de inversión. Este pico es más importante para el dispositivo que tiene la menor movilidad y la más alta concentración de N.

en la capa interfacial y la interfaz.

Podemos concluir que con cualquiera de los procesamientos optimizados es posible alcanzar un EOT subnanométrico. Ante este resultado surge una pregunta: ¿es el efecto sobre la movilidad el mismo en los dos casos?

# Compromiso EOT/Movilidad por varios procesamientos optimizados

En ésta última parte intentamos comparar la movilidad entre los dos tipos de dispositivos estudiados en los párrafos precedentes: FuSi/HfSiON y MG/HfO $_2$ .

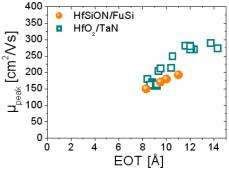

En términos de EOT encontramos una movilidad muy parecida (difiere de 15 %) para el mismo EOT (Figura 5). Tenemos que indicar que el método de extracción usado para los dispositivos FuSi fue más preciso que para los dispositivos MG, y que el dopaje del canal para los MG no fue tan precisamente controlado como en el caso de los dispositivos FuSi. De hecho para los dispositivos FuSi usamos el método de RF-split CV en el que no hay impresiciones por corrientes de fuga a traves la compuerta. Entonces esta diferencia se debe probablemente a un error de medición. Bajo el punto de vista físico tenemos que mostrar la movilidad en función de la

Figura 5: El pico de movilidad efectiva se reduce con la reducción del EOT en cualquier procesamiento. Obtenemos un EOT sub-nanométrico con un procesamiento hecho con un "thermal budget" alto o estandar.

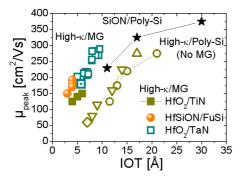

IOT (o espesor de la capa de SiO<sub>2</sub>). La razón es que los efectos Coulómbicos de los defectos disminuyen con el aumento del efecto de apantallamiento. Este efecto de apantallamiento proviene de una parte de los átomos de metal en la compuerta (Ni, Ta y Ti) y de otra parte con el espesor del IOT [27]. Tenemos que comparar los efectos de las cargas (defectos) que degradan la movilidad en función de los efectos de apantallamiento. Entre FuSi y MG la magnitud del apantallamiento es igual como lo hemos mostrado en [34]. Si comparamos con la misma IOT podemos deducir cual dispositivo o procesamiento genera más defectos debido a la concentración de Hf o de N. En la Figura 6, podemos ver que los dispositivos realizados con un procesamiento optimizado de tipo MG (con TaN/TiN) o de tipo FuSi (NiSi) siguen la misma tendencia y en consecuencia obedecen a la misma variación del IOT o del efecto de apantallamiento.

Podemos suponer que los efectos de carga son independientes del procesamiento usado. La reducción del EOT con N por el HfSiON genera una densidad de defectos igual a la de un dispositivo HfO<sub>2</sub> que tiene por naturaleza más defectos. Para concluir esta parte podemos decir que la reducción de escala por medio de un procesamiento optimizado particular (que sea de bajo/alto presupuesto térmico o "thermal budget" y con alta/baja

| Samples | IL[nm] | HfSiON[nm] | DPN  | PNA  | EOT [Å] |

|---------|--------|------------|------|------|---------|

| S1      | 0.5    | 1.7        | DPN2 | PNA1 | 10      |

| S2      | 0.5    | 1.7        | DPN1 | PNA1 | 9.5     |

| S3      | 0.5    | 2.3        | DPN1 | PNA1 | 11      |

| S4      | 0.5    | 2.3        | DPN1 | PNA2 | 8.3     |

Tabla 2: Diferentes parámetros de procesamientos para las muestras usadas en este esdudio. DPN1: potencia de RF es 1750W, presión 8mT, f=10kHz,  $DC=20\,\%$  y la duración 20s, DPN2 es más suave que DPN1, es decir con menor DC (5 %). PNA1: T=900 °C durante 15 s bajo  $O_2$  a presión cercana a 0.5 T. PNA2 es más suave que PNA1 es decir con menor  $O_2$  presión (0.1 % de 0.5 T).

Figura 6: La redución del IOT enseña como se reduce el efecto de apantallamiento. La redución del pico de la movilidad se explica como una reducción de este efecto y es universal para cualquier tipo de dieléctrico. Obtenemos la misma tendencia entre los dos procesamientos (FuSi o MG) sugiriendo que para un EOT menor de 1nm la densidad de defecto en el film no está controlada. Los datos de la movilidad para los dispositivos con compuerta de PolySi y TiN (únicamente) [7].

concentración de N) no tiene efecto sobre el desempeño de la movilidad y del EOT del MOSFET. En otras palabras, bajo 1nm no es posible controlar la calidad de materiales de interfaces o de las capas de materiales high- $\kappa$  y SiON. En consecuencia no podemos controlar el desempeño del MOSFET a esta escala con las técnicas de deposición que son la más usadas en industria (ALD, MOCVD, Nitradation etc.) con un esquema de integración de tipo "gate first". Podemos pensar ahora a cambiar de esquema de integración y usar un procesamiento "gate last" como lo impulsó INTEL [35] y/u orientar las investigación hacia otro material como el Zr.

## **Conclusiones**

En este estudio, hemos enfocado nuestra atención en el impacto de los defectos eléctricos debido a los materiales high- $\kappa$  sobre la movilidad. Dada la simplicidad del modelo semi-empírico que hemos utilizado, podemos entender adecuadamente la degradación de la movilidad. De todos los métodos de procesamientos de materiales high- $\kappa$  hemos elegido dos de los más optimizados y adecuados para el Hf: el MG/HfO2 con activación de unión de tipo SPER y el FuSi/HfSiON con DPN+PNA. En dispositivos de tipo MG/HfO2, si el "thermal budget" es bajo podemos alcanzar un EOT  $\approx$ 0.8 nm gracias a la valor  $\kappa$  del HfO2 y a la reducción del recrecimiento de IOT. Pero el problema surge también del HfO2 que genera una interface de mala calidad con el SiO2 además de defectos dentro el Hf. Aunque la temperatura

queda dentro del limite de recristalización, la reducción del IOT, que disminuye el efecto de apantallamiento, puede explicar la caída de la movilidad cuando alcanzamos un EOT ≈0.8 nm. Con dispositivos hechos con FuSi/HfSiON, la estabilidad es mucho mejor así que el problema de defectos eléctricos debería ser menos importante. No obstante, el uso de condiciones de nitridación optimizada permite alcanzar un dispositivo con EOT  $\approx$ 0.8 nm y con un "thermal budget" alto o estándar (Spike) lo que fue considerado imposible con HfSiON en el pasado. Pero el uso exagerado del N para reducir el EOT puede generar un cambio de la naturaleza de la pila HfSiON/SiO<sub>2</sub>. De hecho el SiO<sub>2</sub> se vuelve probablemente SiON y el HfSiON se encuentra con un valor de  $\kappa$  mucho más alto de lo que conocemos. Solo una caracterización física ("High Resolution-Transmission Electronic Microscopy", "Fourier Transform Infra-Red" y "Elastic Recoil Detection Analisys") podría aclarar esta modificación de la naturaleza de la pila del dispositivo; para esto es necesario usar instrumentos con una precisión de 0.3-0.5 nm. Entonces, reducir el EOT a escala nanometrica resulta en una degradación de la movilidad que perjudica al funcionamiento del MOSFET como lo hemos mostrado.

Finalmente hemos comparado la movilidad de los dos dispositivos con la variación del IOT y resultó que con un método ó con el otro no podemos controlar la degradación de la movilidad, es decir la calidad de las interfaces materiales bajo 1 nm con las muy usadas técnicas de procesamiento (ALD y MOCVD) con el esquema de integración donde la deposición del high- $\kappa$  es anterior a la activación de las uniones ("gate first"). Entonces la optimización del procesamiento para reducir el EOT no es compatible con el desempeño de la movilidad para los dispositivos high- $\kappa$  hechos con Hf. Las industrias pueden usar un "thermal budget" estándar (1050 °C) para lograr el mismo desempeño que un dispositivo con un procesamiento más "exótico", es decir con una activación de unión de tipo SPER que daña la calidad y la resistividad de las uniones (control del desempeño de los MOSFET de canal corto  $\approx 50 - 30$  nm) [36]. Por otro lado, si queremos aumentar la movilidad por el medio de la calidad del film para los MOSFET con EOT subnanométrico tenemos que investigar otro tipo de esquema de integración como el "gate last" o investigar otro material como el Zr.

### Agradecimientos

Los autores agradecen al AMSIMEC, donde se realizaron los experiemtos, y L.-Å. Ragnarsson y A. Rothschild en IMEC por su valiosa ayuda y por haber permitido usar sus muestras.

#### Referencias

- [1] Arns, R. G. 1998. "The other transistor: early history of the mosfet." *Engineering Sciences Educational Journal*. 233–240.

- [2] Kilby, J. S. 1976. "Applied the miniaturized electronic circuits." *IEEE Transaction of Electron Devices*. 23, 648–654.

- [3] Moore, G. 1965. "Cramming more components onto integrated circuits." *Electronics Magazine*.

- [4] Dennard, R. H., Gaensslen, F. H., Yu, H.-N., Rideout, V. L., Bassous, E., and Leblanc, A. R. 1974. "Design of ion-implanted mosfet's with very small physical dimensions." *IEEE Journal of Solid-State Circuits*. SC-9, n. 5.

- [5] Wilk, G. D., Wallace, R. M., and Anthony J. M. 2001. "High- $\kappa$  gate dielectrics: current status and materials properties considerations." *Journal of Applied Physic*. 89, 5243–5275.

- [6] Tsai, W., Ragnarsson, L.-A., Chen, P. J., Onsia, B., Carter, R., Cartier, E., Young, E., Green, M., Caymax, M., Gendt, S. D., and Heyns, M. 2003. "Comparison of sub 1 nm TiN/HfO<sub>2</sub> with Poly-Si/HfO<sub>2</sub> gate stacks using scaled chemical oxide interfaces." *International Symposium on VLSI Technology*.

- [7] Ragnarsson, L.-A., Pantisano, L., Kaushik, V., Saito, S.-I., Shimamoto, Y., Gendt, S. D., and Heyns, M. 2003. "The impact of sub-monolayers of HfO<sub>2</sub> on the device performance of high-κ based transistors." *IEEE International Electron Devices Meeting (IEDM)*.

- [8] Hiratani, M., Saito, S.-I., Shimamoto, Y., and Torii, K. 2001. "Effective electron mobility reduced by remote charge scattering in high-κ gate stacks." *Japanese Jour*nal of Applield Physic (JJAP). 41, 4521–4522.

- [9] Kirsch, P. D., Quevedo-Lopez, M. A., Krishnan, S. A., Lee, B. H., Pant, G., Kim, M. J., Wallace, R. M., and Gnade, B. E. 2006. "Relationship of HfO2 Material Properties and Transistor Performance." IEEE International Symposium on VLSI technology, Honolulu, HI, USA, 1-2.

- [10] Langenbuch, M., Bottini, R., Vitali, M., and Ghidini, G. 2005. "In situ steam generation (issg) versus standard steam technology: impact on oxide reliability." *Microelectronics and Reliability*. 45, 875–878.

- [11] Shi, X. 2006. "Development of 300mm MOCVD  $HfSiO_x$  process?" *ECS Transactions*, **3**.

- [12] Rothschild, A., Shi, X., Everaert, J., Kerner, C., Chiarella, T., Hoffmann, T., Vrancken, C., Shickova, A., Yoshinao, H., Mitsuhashi, R., Niwa, M., Lauwers, A., Veloso, A., Kittl, J., Absil, P., and Biesemans, S. 2007. "Achieving 9ps unloaded ring oscillator delay infusi/hfsion with 0.8 nm EOT." Symposium on VLSI Technology. 198–199.

- [13] Kittl, J., Veloso, A., Lauwers, A., Anil, G., Demeurisse, C., Kubicek, S., Niwa, M., Dale, M. J. H. V., Richard, O., Pawlak, M. A., Jurczak, M., Vrancken, C., Chiarell, T., Brus, S., Maex, K., and Biesemans, S. 2005. "Scalability of Ni-FuSi gate processes: phase and V<sub>t</sub> control to 30nm gate length" *IEEE International Symposium on VLSI technology*.

- [14] Smedt, F. D., Vinckier, C., Cornelissen, I., Gendt, S. D., and Heyns, M. 2000. "A detailed study on the growth of thin oxide layers on silicon ozonated solutions." *Journal* of the Electrochemical Society. 147(3), 1124–1129.

- [15] Kim, Y., Tuominen, M., Raaijmakers, I., deBlank, R., Wilhelm, R., and Haukka, S. 2000. "Initial stage of the ultra-thin oxide growth in water vapor on Si<100>surface" *Electrochemical and Solid State Let*ters, 3, 346.

- [16] Yamamoto, W. D., Aoulaiche, M., Houssa, M., Gendt, S. D., Horii, S., Asai, M., Sano, A., Hayashi, S., and Niwa, M. 2006. "Electrical and physical characterization of remote plasma oxidized HfO<sub>2</sub> gate dielectrics." *IEEE Transactions on Electron Devices*. 53, 1153–1157.

- [17] Trojman, L., Ragnarsson, L.-A., O'Sullivan, B. J., Rosmeulen, M., Kaushik, V., Groeseneken, G. G., Maes, H., Gendt, S. D., and Heyns, M. 2007. "High-κ metal gate mosfet's: impact of extrinsic process condition on the gate stack quality a mobility study." *IEEE Transactions on Electron Devices*. 54, 497–507.

- [18] Severi, S., Anil, K. G., Pawlak, J. B., Duffy, R., Henson, K., Lindsay, R., Lauwers, A., Veloso, A., Marneffe, J. F. D., Ramos, J., Camillo-Castillo, R. A., Eyben, P., Dachs, C., Vandervorst, W., Jurczak, M., Biesemans, S., and Meyer, K. D. 2004. "Diffusion-less junctions and super halo profiles for pmos transistors formed by sper andfusi gate in 45 nm physical gate length devices." *IEEE International Electron Devices Meeting (IEDM)*. 99–102.

- [19] Hoffmann, T., Veloso, A., Lauwers, A., Yu, H., Tigelaar, H., Dal, M. V., Chiarella, T., Kerner, C., Kauerauf, T., Shickova, A., Mitsuhashi, R., Satoru, I., Niwa, M., Rothschild, A., Froment, B., Ramos, J., Nackaerts, A., Rosmeulen, M., Brus, S., Vrancken, C., Absil, P. P., Jurczak, M., Biesemans, S., and Kittl, J. A. 2004. "Nibasedfusi gates: Cmos integration for 45nm node and beyond." *IEEE International Electron Devices Meeting (IEDM)*.

- [20] Takagi, S.-I., Toriumi, A., Iwase, M., and Tango, H. 1994. "On the universality of the inversion layer mobility in Si MOSFET's: Part I - Effects of substrate impurity concentration." *IEEE Transactions on Electron Devices*. 41, 2357-2362.

- [21] Sodini, C. G., Ekstedt, T. W., and Moll, J. L. 1982. "Transistor charge accumulation and mobility in thin dielectric MOS." Solid State Electronic. 25, 833–841.

- [22] San Andrés, E. S., Pantisano, L., Ramos, J., Severi, S., Trojman, L., Gendt, S. D., and Groeseneken, G. 2006. "RF Split capacitance-voltage measurements of short-channel and leaky MOSFET devices." *IEEE Electron Device Letters*. 27, 772–774.

- [23] Ragnarsson, L.-A., Severi, S., Trojman, L., Brunco, D. P., Johnson, K. D., Delabie, A., Schram, T., Tsai, W., Groeseneken, G., Meyer, K. D., Gendt, S. D., and

- Heyns, M. 2006. "Electrical characteristics of 8 Å EOT HfO<sub>2</sub>/TaN low thermal-budget n-channel FETs with solid-phase epitaxially regrown junctions." *IEEE Transactions on Electron Devices* 53, 1657-1668.

- [24] Crag, R., Chowdhury, N. A., Bashkaran, M., Swain, P. K., and Misra, D. 2004. "Eletrical characteristics of thermally evaporated HfO<sub>2</sub>." *Journal of the Electrochemical Society.* 151, 215–219.

- [25] Hauser, J. R. and Ahmed, K. 1998. "Characterization of ultra thin oxides using c-v and i-v measurements." In proceeding Characterization and Metrology for ULSI Technology. 235.

- [26] Trojman, L., Ragnarsson, L.-A., Pantisano, L., Lujan, G. S., Houssa, M., Schram, T., Cubaynes, F., Schaekers, M., Ammel, A. V., Groeseneken, G., Gendt, S. D., and Heyns, M. 2005. "Effect of the dielectric thickness and the metal deposition technique on the mobility for HfO<sub>2</sub>/TaN n-MOS devices." *Microelectronic Engineering* 80, 86–89.

- [27] Fischetti, M. V., Neumayer, D., and Cartier, E. November 2001. "Effective electron mobility in si inversion layers in metal-oxide-semiconductor systems with a high-κ insulator: The role of remote phonon scattering." *Journal of Applied Physics*. 90, 4587–4608.

- [28] Jeon, D. S. and Burk, D. E. 1989. "MOSFET electron inversion layer mobilities a physically based semi-empirical model for a wide temperature range." *IEEE Transactions on Electron Devices*. 36, 1456–1463.

- [29] "The International Technology Roadmap for Semiconductors." www.itrs.org

- [30] Garros, X., Besson, P., Reimbold, G., and Boulanger, F. 2008. "Impact of the crystallinity of high- $\kappa$  oxides on  $v_t$  instabilities of nmos devices assessed by physical and electrical measurements." *IEEE International Reliability Physic Symposium.* 330–334.

- [31] Lysaght, P. S., Foran, B., Bersuker, G., Chen, P. J., Murto, R. W., and Huff, H. R. February 2003. "Physicochemical properties of the HfO<sub>2</sub> in response to rapid thermal anneal." *Applied Physic Letters*. 82, 1266–1268.

- [32] Schram, T., Ragnarsson, L.-A., Lujan, G., Deweerd, W., Chen, J., Tsai, W., Lander, R., Benson, K., Hooker, J., Vertommen, J., Meyer, K. D., Gendt, S. D., and Heyns, M. 2005. "Performance improvement of selfaligned HfO<sub>2</sub>/TaN and SiON/TaN n-MOS transistor." *Microelectronic Reliability*. 45, 779–782.

- [33] Garros, X., Casse, M., Reimbold, G., Rafik, M., Martin, F., Andrieu, F., Cosnier, V., and Boulange, F. 2009. "Performance and reliability of advanced high-κ/metal gate stacks." *Microelectronic Engineering*. 86, 1609–1614.

- [34] Pantisano, L., Trojman, L., Severi, S., Andres, E. S., Kerner, C., Veloso, A., Ferain, I., Hoffman, T., Groeseneken, G., and Gendt, S. D. 2007. "Line width dependent mobility in high-κ a comparative performance study betweenfusi and tin." In proceeding of International Symposium on VLSI Technology, Systems, and Applications (VLSI-TSA).

- [35] Mistry, K., Allen, C., Auth, C., Beattie, B., Bergstrom, D., Bost, M., Brazier, M., Buehler, M., Cappellani, A., Chau, R., Choi, C.-H., Ding, G., Fischer, K., Ghani, T., Grover, R., Han, W., Hanken, D., Hattendorf, M., He, J.,

- Hicks, J., Huessner, R., Ingerly, D., Jain, P., James, R., Jong, L., Joshi, S., Kenyon, C., Kuhn, K., Lee, K., Liu, H., Maiz, J., McIntyre, B., Moon, P., Neirynck, J., Pae, S., Parker, C., Parsons, D., Prasad, C., Pipes, L., Prince, M., Ranade, P., Reynolds, T., Sandford, J., Shifren, L., Sebastian, J., Seiple, J., Simon, D., , and Sivakumar, S. 2007. "A 45nm logic technology with high-κ+metal gate transistors, strained silicon, 9 cu interconnect layers, 193nm dry patterning, and 100 % pb-free packaging." *IEEE International Electron Devices Meeting(IEDM)*. 247–250.

- [36] Trojman, L., Pantisano, L., Dehan, M., Ferain, I., Severi, S., Maes, H. E., and Groeseneken, G. 2009. "Velocity and Mobility Investigation in 1nm-EOT HfSiON on Si (110) and (100) Does the Dielectric Quality Matter?" *IEEE Transactions on Electron Devices*. 56, 3009–3018.